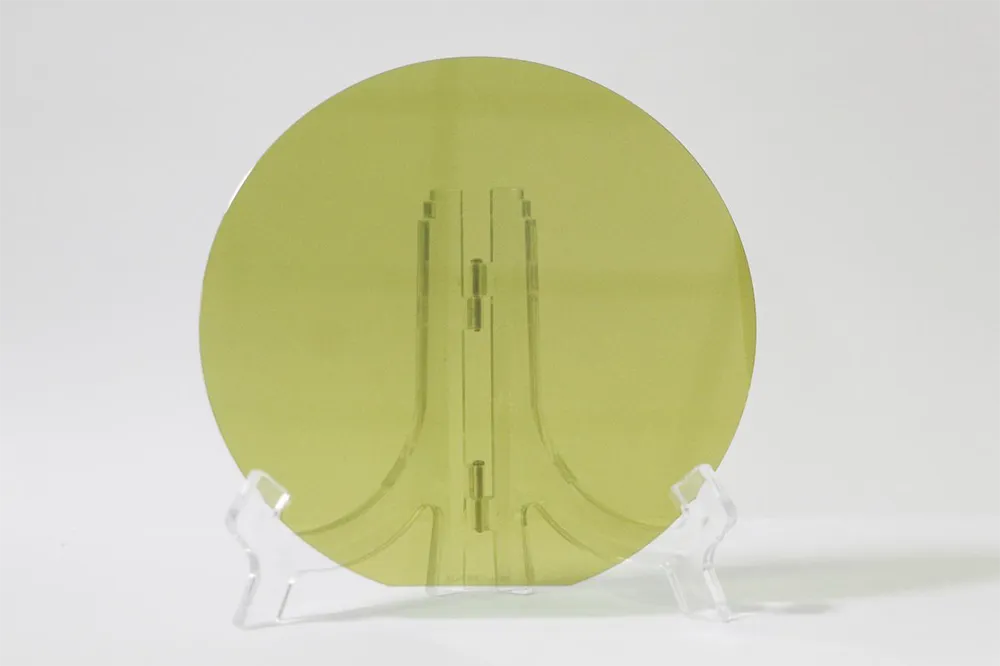

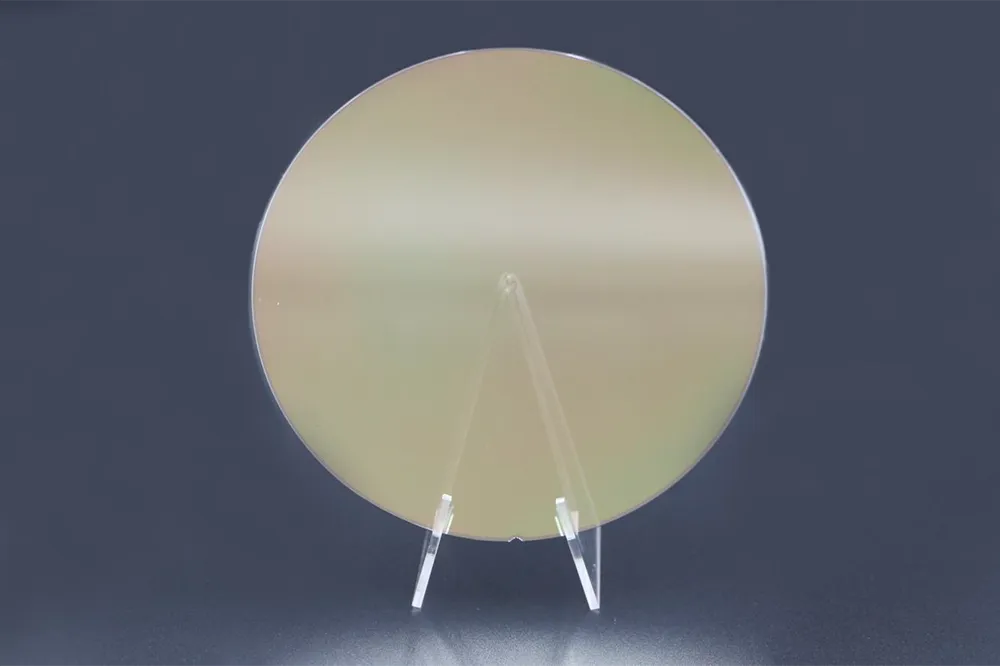

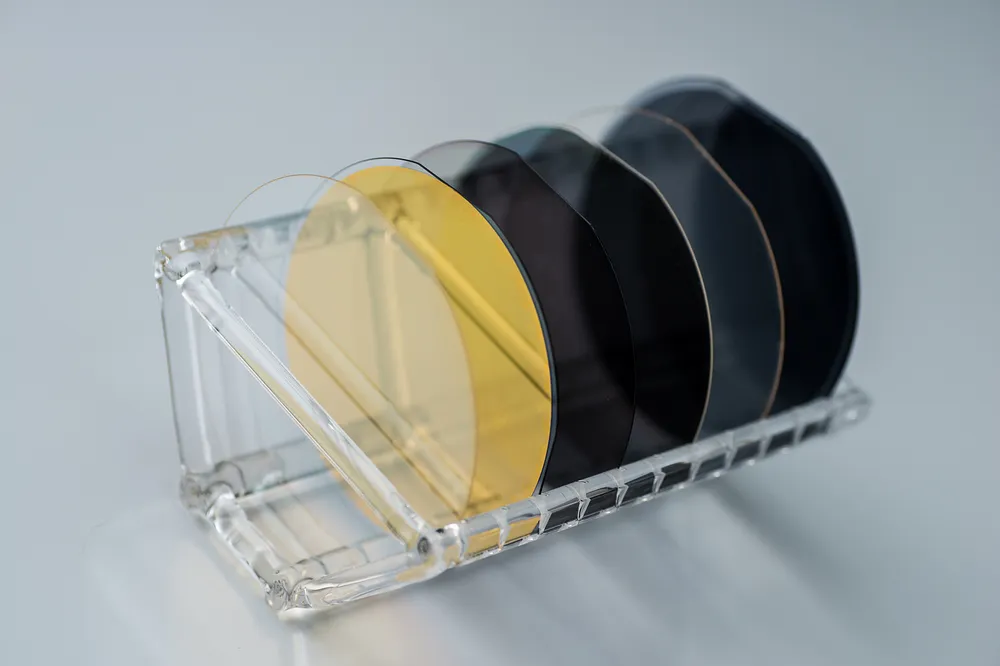

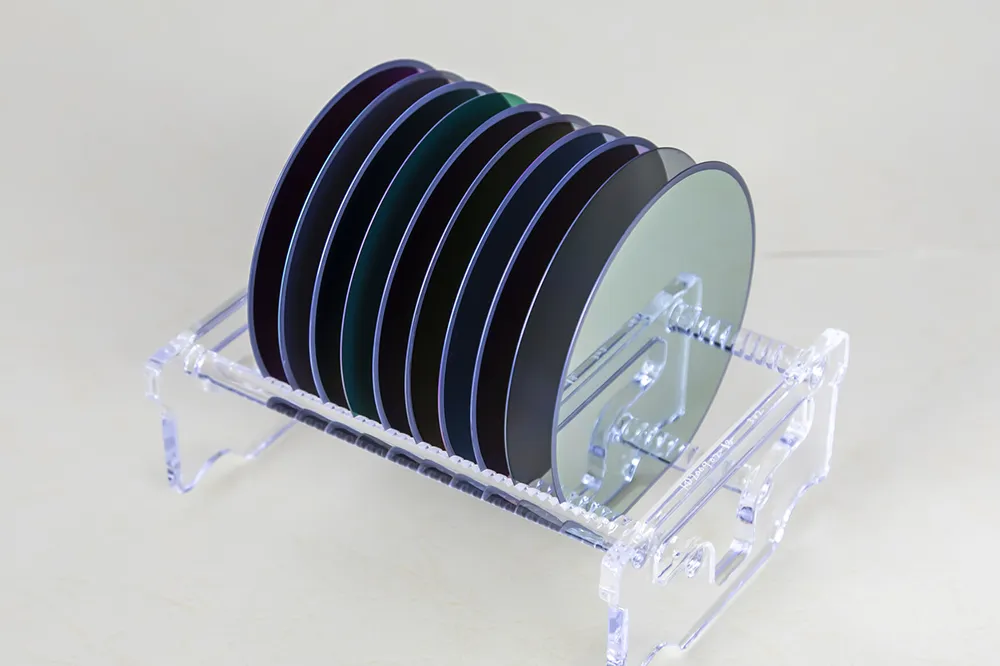

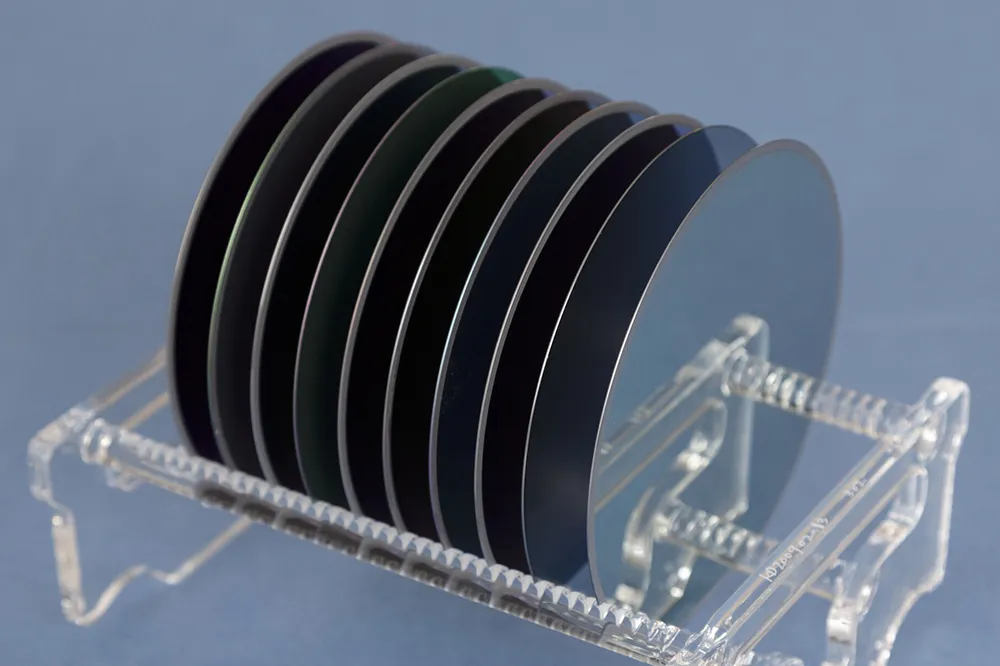

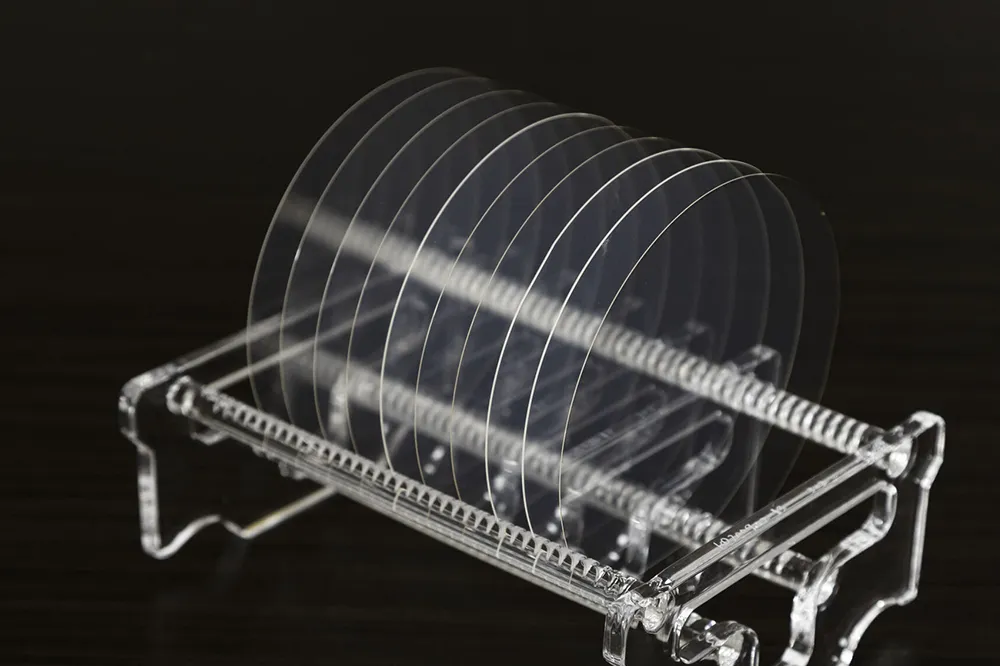

複合ウェーハ

N型SiC複合ウェーハ

| 項目 | 仕様 | 項目 | 仕様 |

|---|---|---|---|

| Diameter | 150 ± 0.2 mm | Front (Si-face) roughness | Ra ≤ 0.2 nm (5 μm × 5 μm) |

| SiC Type | 4H | Edge Chip, Scratch, Crack (visual inspection) | None |

| SiC Resistivity | 0.015–0.025 Ω·cm | TTV | ≤3 μm |

| Transfer layer Thickness | ≥0.4 μm | Warp | ≤35 μm |

| Void | ≤5 ea/wafer (2 mm > D > 0.5 mm) | Thickness | 350 μm ± 25 μm |

半絶縁SiC複合ウェーハ

| 項目 | 仕様 | 項目 | 仕様 |

|---|---|---|---|

| Diameter | 150 ± 0.2 mm | Front (Si-face) roughness | Ra ≤ 0.2 nm (5 μm × 5 μm) |

| SiC Type | 4H | Edge Chip, Scratch, Crack (visual inspection) | None |

| SiC Resistivity | 0.015–0.025 Ω·cm | TTV | ≤3 μm |

| Transfer layer Thickness | ≥0.4 μm | Warp | ≤35 μm |

| Void | ≤5 ea/wafer (2 mm > D > 0.5 mm) | Thickness | 500 ± 25 μm |

N型SiC on Si複合ウェーハ

| 項目 | 仕様 | 項目 | 仕様 |

|---|---|---|---|

| Diameter | 150 ± 0.2 mm | Si Orientation | <111>/<100>/<110> |

| SiC Type | 4H | Si Type | P/N |

| SiC Resistivity | 0.015–0.025 Ω·cm | Flat length | 47.5 ± 1.5 mm |

| Transfer SiC layer Thickness | ≥0.1 μm | Edge Chip, Scratch, Crack (visual inspection) | None |

| Void | ≤5 ea/wafer (2 mm < D < 0.5 mm) | TTV | ≤5 μm |

| Front roughness | Ra ≤ 0.2 nm (5 μm × 5 μm) | Thickness | 500/625/675 ± 25 μm |

半絶縁SiC on Si複合ウェーハ

| 項目 | 仕様 | 項目 | 仕様 |

|---|---|---|---|

| Diameter | 150 ± 0.2 mm | Si Orientation | <111>/<100>/<110> |

| SiC Type | 4H | Si Type | P/N |

| SiC Resistivity | ≥1E8 Ω·cm | Flat/Notch | Flat/Notch |

| Transfer SiC layer Thickness | ≥0.1 μm | Edge Chip, Scratch, Crack (visual inspection) | None |

| Void | ≤5 ea/wafer (2 mm > D > 0.5 mm) | TTV | ≤5 μm |

| Front roughness | Ra ≤ 0.2 nm (5 μm × 5 μm) | Thickness | 500/625/675 ± 25 μm |

Si on SiC複合ウェーハ

| 項目 | 仕様 | 項目 | 仕様 |

|---|---|---|---|

| Diameter | 150 ± 0.2 mm | SiC Type | 4H |

| Si Orientation | <111>/<100>/<110> | SiC Resistivity | 0.015–0.025/≥1E8 Ω·cm |

| Si Type | P/N | Flat/Notch | Flat/Notch |

| Transfer Si layer Thickness | ≥0.1 μm | Edge Chip, Scratch, Crack (visual inspection) | None |

| Void | ≤5 ea / wafer (2 mm > D > 0.5 mm) | TTV | ≤5 μm |

| Front roughness | Ra ≤ 0.2 nm (5 μm × 5 μm) | Thickness | 350/500 ± 25 μm |

Si on AlN複合ウェーハ

| 項目 | 仕様 | 項目 | 仕様 |

|---|---|---|---|

| Diameter | 150 ± 0.2 mm | AlN Resistivity | ≥1E8 Ω·cm |

| Si Orientation | <111>/<100>/<110> | AlN Thermal conductivity | ≥180 W/m·K |

| Si Type | P/N | Flat length | 47.5 ± 1.5 mm |

| Transfer Si layer Thickness | ≥0.1 μm | TTV | ≤5 μm |

| Edge Chip, Scratch, Crack (visual inspection) | None | Thickness | 625 ± 25 μm |

| Front roughness | Ra ≤ 0.2 nm (5 μm × 5 μm) |

SOIウェーハ

| サイズ | inch | 4 | 5 | 6 | 8 | 12 |

|---|---|---|---|---|---|---|

| 活性層 | Unit | 仕様 | ||||

| 製法 | - | CZ/FZ | ||||

| タイプ・導電型 | - | P/N/ノンドープ | ||||

| 結晶方位 | - | <100>/<111>/<110> | ||||

| ドーパント | - | B、P、As、Sb | ||||

| 厚み | μm | ≧1.0 | ||||

| *抵抗率 | Ω・cm | 0.001–10000 | ||||

| *埋込み酸化膜 | μm | 0.05–10 | ||||

| 支持基板 | 仕様 | |||||

| 製法 | - | CZ/FZ | ||||

| タイプ・導電型 | - | P/N/ノンドープ | ||||

| 結晶方位 | - | <100>/<111>/<110> | ||||

| ドーパント | - | B、P、As、Sb | ||||

| *厚み | μm | JEITA・SEMI標準/200-1500 | ||||

| *抵抗率 | Ω・cm | 0.001–10000 | ||||

| 備考 | *詳細仕様は別途お問合せ下さい | |||||

300~900nm LiNbO3単結晶薄膜(LNOI)

● Lithium Niobate Thin Film

● SiO2

● Si, LN, Quartz, Fused Silica, etc.

| トップ機能層 | 直径 | 3, 4, (6) インチ | 方位 | X, Z, Y 他 |

|---|---|---|---|---|

| 材料 | LiNbO3 | 厚さ | 300~900 nm | |

| ドーピング(オプション) | MgO | |||

| 分離層 | 材料 | SiO2 | 厚さ | 1000~4000 nm |

| 基板 | 材料 | Si, LN, 水晶, 溶融石英 他 | ||

| 厚さ | 400~500 μm | |||

| オプションの電極層 | 材料 | Pt, Au, Cr | 厚さ | 100~400 nm |

| 構造 | SiO2分離層の上または下 | |||

300~900nm LiTaO3単結晶薄膜(LTOI)

● Lithium Tantalate Thin Film

● SiO2

● Silicon

| トップ機能層 | 直径 | 3, 4, 6 インチ | 方位 | Y-42, Y-46.3, Z 他 |

|---|---|---|---|---|

| 材料 | LiTaO3 | 厚さ | 300~900 nm | |

| 分離層 | 材料 | SiO2 | 厚さ | 300~4000 nm |

| 基板 | 材料 | Si | ||

| 厚さ | 400~500 μm | |||

Si基板5~50um LT & LN 薄膜

● Lithium Tantalate Thin Film

● Silicon

● Lithium Niobate Thin Film

● SiO2

● Silicon, Quartz, etc.

| トップ機能層 | 直径 | 3, 4, 6 インチ | 方位 | Y-42, Y-46.3, Z 他 |

|---|---|---|---|---|

| 材料 | LiTaO3 | 厚さ | 300~900 nm | |

| 分離層 | 材料 | SiO2 | 厚さ | 300~4000 nm |

| 基板 | 材料 | Si | ||

| 厚さ | 400~500 μm | |||

20~60μm極薄、超平坦ウエハー

● Lithium Tantalate Thin Film Or Lithium Niobate Thin Film

| 直径 | 3, 4 インチ | 方位 | X, Y, Z 他 |

| 厚さ | 10~60 μm | 材料 | LN, LT, Si 他 |

| 表面 | 両面あるいは片面研磨 | ||

オーダーメイドLN & LT薄膜

| トップ層/詳細 | 基板詳細 | トップ層薄膜詳細 | ||||||

| 多層構造 | 電極&導波路パターン | 異なる材料(SiO2/Si, Si, サファイア, 石英 他) | PPLN | 特殊サイズ | 電極(Au, Pt, Cr, Al 他) | 方位(バルクウエハーと同様) | ドーピング(MgO, Fe, Er, Tm 他) | |

| 100~1000 nm LiNbO3 | √ | √ | √ | √ | √ | √ | √ | √ |

| 100~1500 nm LiTaO3 | √ | √ | √ | √ | √ | √ | √ | |

| 5~50 μm LiNbO3 | √ | √ | √ | √ | ||||

| 5~50 μm LiTaO3 | √ | √ | √ | √ | ||||